公司名称:誉诚(深圳)实业科技有限公司

详细说明

VREG, BOR, PORAlthough the core and I/O circuitry operate on two different voltages, these devices have an on-chipvoltage regulator (VREG) to generate the VDD voltage from the VDDIO supply. This eliminates the cost andspace of a second external regulator on an application board. Additionally, internal power-on reset (POR)and brown-out reset (BOR) circuits monitor both the VDD and VDDIO rails during power-up and run mode.2.8.1On-chip Voltage Regulator (VREG)A linear regulator generates the core voltage (VDD) from the VDDIO supply. Therefore, although capacitorsare required on each VDD pin to stabilize the generated voltage, power need not be supplied to these pinsto operate the device. Conversely, the VREG can be disabled, should power or redundancy be theprimary concern of the application.2.8.1.1Using the On-chip VREGTo utilize the on-chip VREG, the VREGENZ pin should be tied low and the appropriate recommendedoperating voltage should be supplied to the VDDIO and VDDA pins. In this case, the VDD voltage needed bythe core logic will be generated by the VREG. Each VDD pin requires on the order of 1.2 μF (minimum)capacitance for proper regulation of the VREG. These capacitors should be located as close as possibleto the VDD pins.2.8.1.2Disabling the On-chip VREGTo conserve power, it is also possible to disable the on-chip VREG and supply the core logic voltage tothe VDD pins with a more efficient external regulator. To enable this option, the VREGENZ pin must be tiedhig

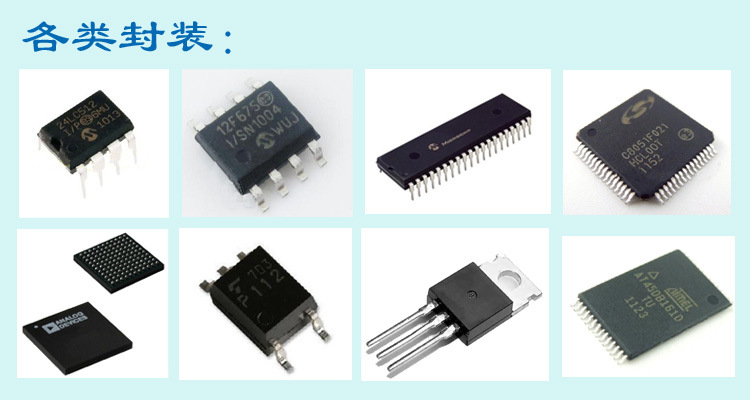

公司产品信息

0-5V转0-5V电量信号隔离器/安全栅0-5V隔离器/一进二出分配器

4-20mA/0-5V/0-10v转0-3v导轨隔离器

0-75mV转0-5V信号放大器/安全栅

STM32L152CBT6 托盘/STM8L151R8T6 托盘

0-10V转232/模拟信号转232/485

MSP430F2001IPWR/MSP430F123IDWR

0-20mA信号隔离器/安全栅

10mA/0-20mA转0-5KHz常规参数变送器

0-75mV转0-10V电压/电量分配转换器

MSP430F2122TRHBT/MSP430F2012IRSAT

STM8S208MBT6B 托盘/STM32L151RCT6 托盘

TM4C1230D5PMI/MSP430F5152IRSBR

MSP430F1611IPMR/MSP430F169IPMR

STM8S207RBT6C 托盘/STM8S208R8T6

MSP430G2403IRHB32T/MSP430F6721IPN

0-5V转4-20ma信号隔离器/基础常规信号

0-5V转5V电压脉冲/安全栅

MSP430F5327IPNR/MSP430F5510IPTR

MSP430F5510IRGCR/TMS320F28335ZJZA

誉诚(深圳)实业科技有限公司

联系人:朱小姐 女士 (销售)

电 话:0755-29309513

传 真:0755-29309513

手 机:13560767759

Q Q:

地 址:中国广东深圳市深圳市前海深港合作区前湾一路1号A栋201室

邮 编:

网 址:http://siruitegs.qy6.com(